Матричные переключатели, выполненные в виде интегральных микросхем

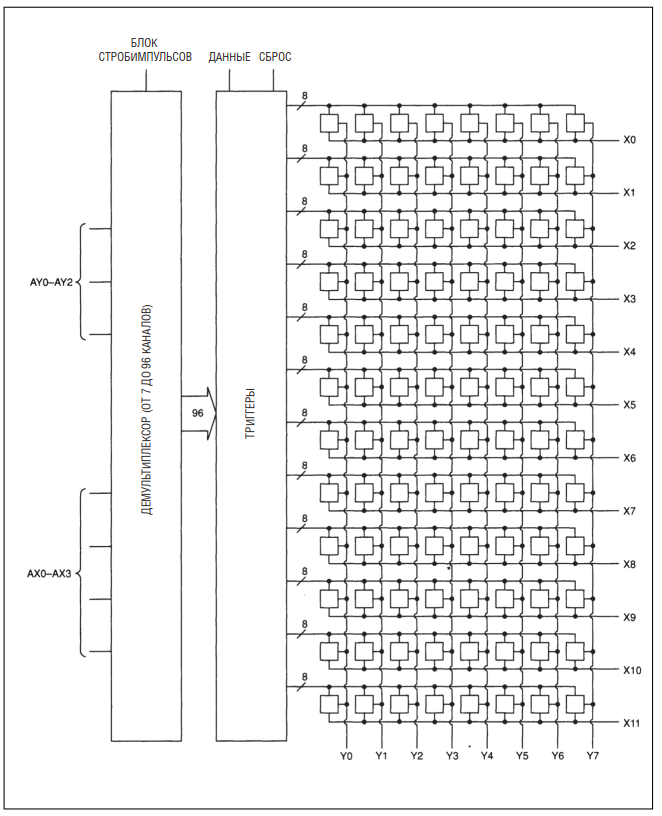

Компания Silicon Systems Inc. производит матричный переключатель из 96 элементов SSI 78A093, который формирует матрицу из 12*8 элементов, изображенную на рис. 7.21.

Рис. 7.21.Блок-схема интегральной микросхемы SSI 78A093

Семь адресных линий (три адресные линии рядов, с AY0 по AY2, и четыре адресные линии строк, с AX0 по AX3) обеспечивают под микропроцессорным управлением доступ к каждому из 96 коммутируемых элементов. Конкретный коммутируемый элемент выбирается путем поступления на элемент соответствующего адреса ряда и строки. Информация о разомкнутом состоянии (Откл.) или замкнутом (Вкл.) вводится через вывод Data (данные) и фиксируется положительным импульсом в цепи стробирующего импульса. Если на выводе Data присутствует логический сигнал низкого уровня, стробирующий импульс отключит адресный блок, и наоборот.

Матричный переключатель, выполненный в виде интегральной микросхемы, обладает большим количеством преимуществ перед своим релейным предшественником. Прежде всего, из-за использования в интегральной микросхеме КМОП-структур его отличает очень малый уровень энергопотребления (менее 100 нВт на отдельный элемент). Аналоговые коммутируемые системы обеспечивают более чем на –92 дБ ослабление перекрестных помех, величину сопротивления цепи во включенном состоянии всего лишь в 28 Ом и практически не вносят никаких искажений в сигнал.

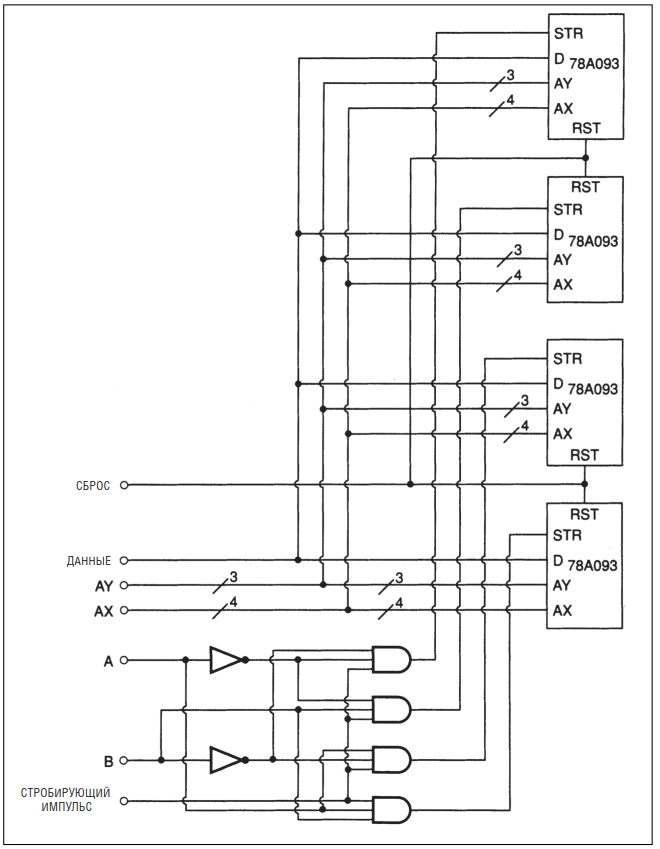

Самым простым способом использования матричных переключателей является их тандемное применение с включением цепи искателя для управления стробирующим сигналом. На рис. 7.22 приведен пример схемы многоматричного переключателя.

Рис. 7.22.Применение матричного переключателя

Дата добавления: 2022-01-31; просмотров: 758;